1 Terms

1 TermsHome > Terms > English (EN) > reduced instruction set computer (RISC)

reduced instruction set computer (RISC)

A processor architecture that shifts the analytical process of a computational task from the execution or runtime to the preparation or compile time. By using less hardware or logic, the system can operate at higher speeds. RISC cuts down on the number and complexity of instructions, on the theory that each one can be accessed and executed faster, and that less semiconductor real estate is required to process them. The result is that for any given semiconductor technology, a more powerful microprocessor can be produced with RISC than with complex instruction set computer (CISC) architectures.

This simplification of computer instruction sets gains processing efficiencies. That theme works because all computers and programs execute mostly simple instructions. RISC has five design principles:

• Single-cycle execution — In most traditional central processing unit (CPU) designs, the peak possible execution rate is one instruction per basic machine cycle, and for a given technology, the cycle time has some fixed lower limit. Even on complex CPUs, most compiler-generated instructions are simple. RISC designs emphasize single-cycle execution, even at the expense of synthesizing multi-instruction sequences for some less-frequent operations.

• Hard-wired control, little or no microcode — Microcode adds a layer of interpretive overhead, raising the number of cycles per instruction, so even the simplest instructions can require several cycles.

• Simple instructions, few addressing modes — Complex instructions and addressing modes, which entail microcode or multicycle instructions, are avoided.

• Load and store, register-register design — Only loads and stores access memory; all others perform register-register operations. This tends to follow from the previous three principles.

• Efficient, deep pipelining — To make convenient use of hardware parallelism without the complexities of horizontal microcode, fast CPUs use pipelining. An n-stage pipeline keeps up to “n” instructions active at once, ideally finishing one (and starting another) every cycle. The instruction set must be carefully tuned to support pipelining.

- Part of Speech: noun

- Synonym(s):

- Blossary: Information Technology

- Industry/Domain: Technology

- Category: Information technology

- Company: Gartner

- Product:

- Acronym-Abbreviation:

Other Languages:

Member comments

Terms in the News

Billy Morgan

Sports; Snowboarding

The British snowboarder Billy Morgan has landed the sport’s first ever 1800 quadruple cork. The rider, who represented Great Britain in the 2014 Winter Olympics in Sochi, was in Livigno, Italy, when he achieved the man-oeuvre. It involves flipping four times, while body also spins with five complete rotations on a sideways or downward-facing axis. The trick ...

Marzieh Afkham

Broadcasting & receiving; News

Marzieh Afkham, who is the country’s first foreign ministry spokeswoman, will head a mission in east Asia, the state news agency reported. It is not clear to which country she will be posted as her appointment has yet to be announced officially. Afkham will only be the second female ambassador Iran has had. Under the last shah’s rule, Mehrangiz Dolatshahi, a ...

Weekly Packet

Language; Online services; Slang; Internet

Weekly Packet or "Paquete Semanal" as it is known in Cuba is a term used by Cubans to describe the information that is gathered from the internet outside of Cuba and saved onto hard drives to be transported into Cuba itself. Weekly Packets are then sold to Cuban's without internet access, allowing them to obtain information just days - and sometimes hours - after it ...

Asian Infrastructure Investment Bank (AIIB)

Banking; Investment banking

The Asian Infrastructure Investment Bank (AIIB) is an international financial institution established to address the need in Asia for infrastructure development. According to the Asian Development Bank, Asia needs $800 billion each year for roads, ports, power plants or other infrastructure projects before 2020. Originally proposed by China in 2013, a signing ...

Spartan

Online services; Internet

Spartan is the codename given to the new Microsoft Windows 10 browser that will replace Microsoft Windows Internet Explorer. The new browser will be built from the ground up and disregard any code from the IE platform. It has a new rendering engine that is built to be compatible with how the web is written today. The name Spartan is named after the ...

Featured Terms

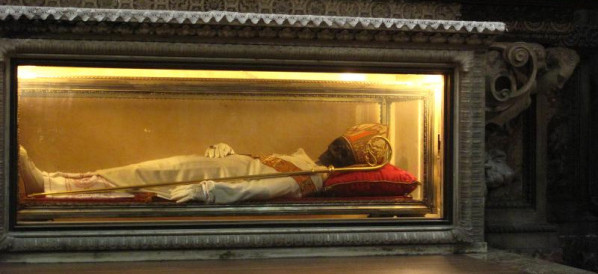

John the Good

John the Good (Latin: Ioannes Bonus, Italian: Giovanni Bono or Buono) was Archbishop of Milan from c. 641 to 669. He is honoured as a Saint in the ...

Contributor

Featured blossaries

Browers Terms By Category

- General astronomy(781)

- Astronaut(371)

- Planetary science(355)

- Moon(121)

- Comets(101)

- Mars(69)

Astronomy(1901) Terms

- Manufactured fibers(1805)

- Fabric(212)

- Sewing(201)

- Fibers & stitching(53)

Textiles(2271) Terms

- Air conditioners(327)

- Water heaters(114)

- Washing machines & dryers(69)

- Vacuum cleaners(64)

- Coffee makers(41)

- Cooking appliances(5)

Household appliances(624) Terms

- Hair salons(194)

- Laundry facilities(15)

- Vetinary care(12)

- Death care products(3)

- Gyms(1)

- Portrait photography(1)

Consumer services(226) Terms

- Economics(2399)

- International economics(1257)

- International trade(355)

- Forex(77)

- Ecommerce(21)

- Economic standardization(2)